1. 半導体製造工程

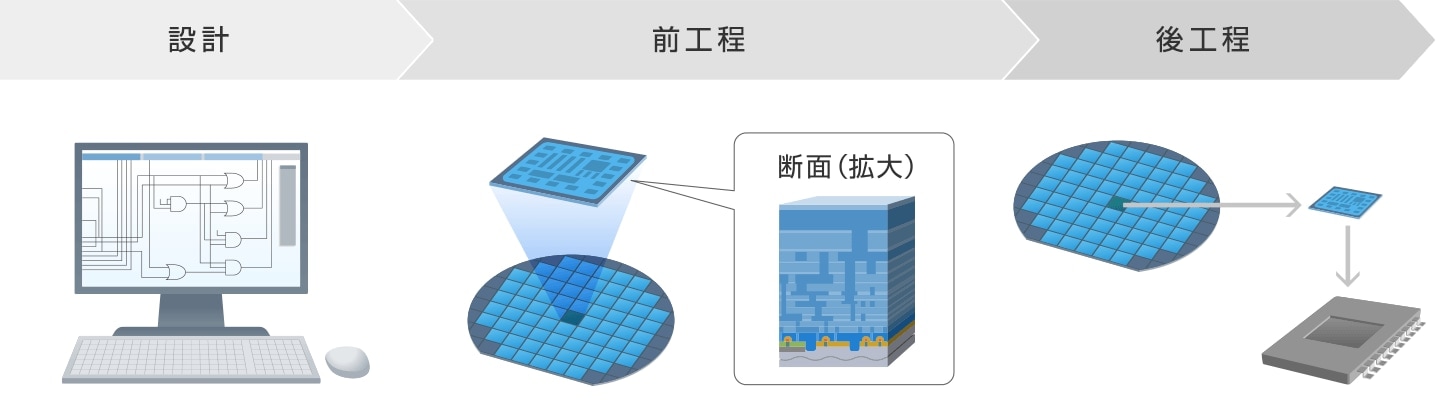

半導体チップは、トランジスタや配線を半導体ウェーハ上に多数形成して電気回路を配置したもので、集積回路(IC、LSI)と呼ばれます。これを作るにはまず、配線回路を設計する必要があります。次に、設計した電子回路を半導体ウェーハ表面に形成する前工程、最後に、チップに切り出して組立てを行う後工程を経て完成します。

ここでは、高精度の加工技術・管理環境が求められる前工程を中心に、半導体の製造工程についてわかりやすくご説明します。

設計

半導体ウェーハ表面に形成されるトランジスタや配線は、非常に細かいため、ウェーハ表面に直接配置することはできません。そこで、フォトマスク(レチクル)と呼ばれる原版にコンピュータを使ってパターンを描き、これをウェーハ上に転写することで、回路を形成します。

設計工程では、仕様に基づいた回路を設計し、フォトマスク(レクチル)を作成します。

-

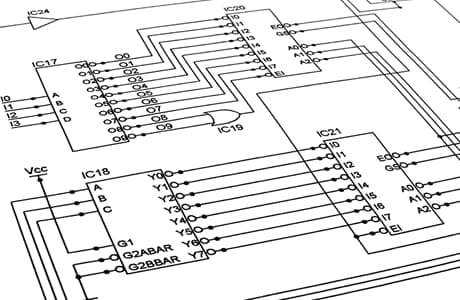

回路/レイアウト設計

必要な機能を実現する回路を設計し、シミュレーションを重ねて効率的なパターンを検討します。

-

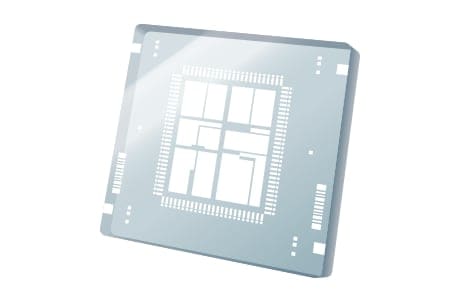

フォトマスク作成

透明なガラス板の表面に実際よりも大きく回路パターンを描いて、半導体ウェーハに転写するための原版(マスター)を作成します。

前工程

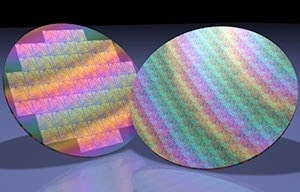

半導体製造工程の「前工程」と呼ばれる半導体ウェーハ処理工程では、シリコンウェーハ表面上にトランジスタなどを含む電子回路を高集積で形成して行きます。

シリコンウェーハは、超高純度に生成されたシリコン単結晶インゴットを薄く切断して作られます。(参考:半導体材料 シリコンについて)

1枚のウェーハ上には、四角い半導体チップが百個以上製造されます。現在は、最大で直径300mmのシリコンウェーハが製造に使われています。今後、最先端のウェーハ製造では、直径450mmのシリコンウェーハも使うよう検討されています。

集積回路形成の基本工程

一層の回路を形成するためには、主に次の3工程を踏む必要があります。

1. 成膜

(deposition)

![]()

配線やトランジスタ等になる薄膜層をウェーハ上に形成します。

2. パターン転写

(exposure)

![]()

薄膜上に感光剤(フォトレジスト)を塗布し、フォトリソグラフィー技術でフォトマスク(レチクル)上の回路パターンを転写します。

3. エッチング

(etching)

![]()

現像されたフォトレジストをマスクにして、エッチングによって、薄膜を配線等の形状に加工します。

これらのほかに、洗浄や検査等の工程を加え、繰り返すことで集積回路は形成されます。

前工程の全体フロー

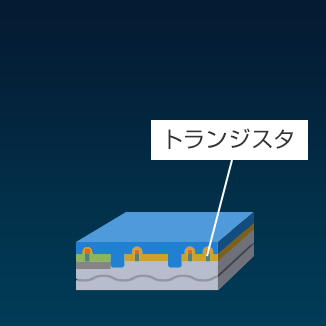

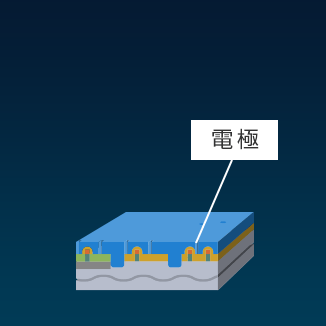

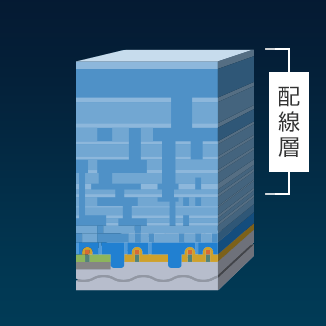

一番下にトランジスタ層を形成し、その上にいくつもの配線回路層を重ねることで、半導体は完成します。

トランジスタ層も配線回路層も、「成膜」「パターン転写」「エッチング」を基本とした精密な加工を繰り返して形成されます。

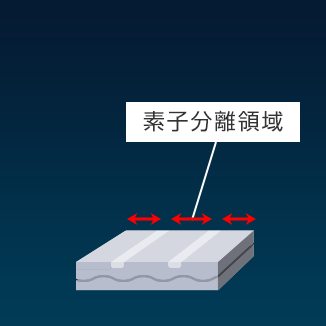

トランジスタが隣接する素子に干渉されずに動作できるよう、素子分離領域を設置して活性領域を区切ります。

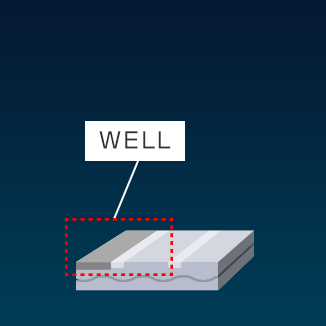

トランジスタを作る領域に、配置するトランジスタに応じた種類・濃度の不純物を注入し、トランジスタを作る準備をします。

後工程

半導体製造工程の「後工程」と呼ばれる組立工程では、ウェーハから半導体を切り出し、所定の位置に固定・封入して検査を行います。

- 半導体の製造1. 半導体製造工程

- 半導体の製造

- 半導体の製造2.半導体の計測と検査

製品サービス