Analysis Method for the CMOS Image Sensor by the Voltage Applied EBAC

ソニーセミコンダクタマニュファクチャリング株式会社

片倉 康雄, 辻田 順彦, 山内 規義, 河村 俊夫

半導体製造工程で発生する不良品を解析し原因究明及びフィードバックすることは製品早期立ち上げや歩留・品質向上において重要であり、解析部署には高い原因判明率が求められる。CMOSイメージセンサでは配線間ShortやGate-LeakなどいわゆるShort系欠陥の判明率が低い傾向にあるため、現行手法より微小領域まで絞り込み可能な新たな解析技術を検討した。解決策として、EBAC法(電子ビーム吸収電流法)の派生技術であり、バイアス印加可能な“電圧印加型-電子ビーム吸収電流法”に着目。検証の結果CMOSイメージセンサの解析に有効であることが分かったので報告する。

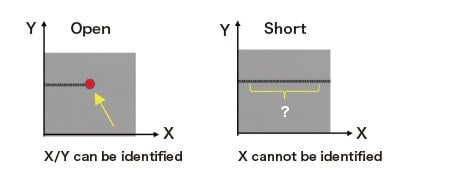

CMOSイメージセンサ製造プロセスは微細化・積層化が進み、様々な欠陥が増加している。このうち配線ShortやGate-LeakなどいわゆるShort系欠陥の原因判明率が、断線などのOpen欠陥と比較して20%近く低い傾向にある。この理由を図1に示す。Open欠陥は画像から欠陥アドレスが特定できるのに対し、Short欠陥は同一ノード全体が画像表示されるためアドレスが絞れないというCMOSイメージセンサ特有の要因である。

図1 Open/Short defect image on CMOS image sensor

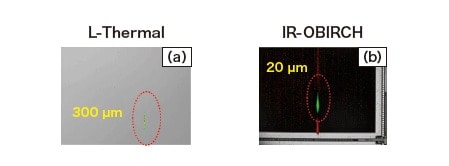

現行の主なShort解析手法は発熱(Lock-In Thermal)やIR-OBIRCHなど光・Laserを用いた解析技術であり、これらはデバイス全体を広範囲で絞り込みできる効果的な手段であるが、後述する要因により分解能が制限される。図2はCMOSイメージセンサの配線Short欠陥を写真(a)L-Thermal、写真(b)IR-OBIRCHで解析した事例である。このように数百~数μ mまでしか絞り込めないため、ここから欠陥箇所を特定するには広範囲のDelayerと平面観察が必要となり、判明率低下の一因となっている。このため新たなShort解析手法構築が急務となっていた。

図2 Image of current optical analysis method

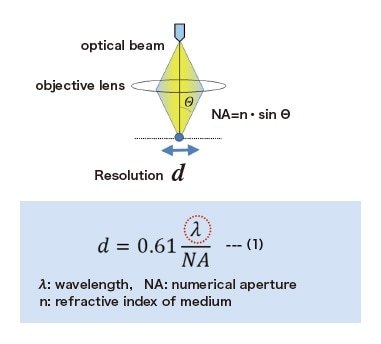

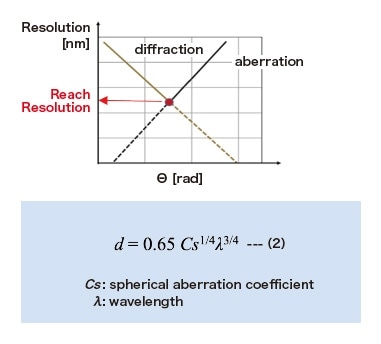

まず検討すべきは高い分解能の実現である。これには回折収差によるBeamの広がりを考察しなければならない。前述光学解析の分解能はRayleighの理論より図3式1で表され、短い波長の入射光を選択することで回折収差が小さくなり分解能が向上する。よって解析装置に搭載される主な光源から光・Laserに加え電子線の波長を考察することにした。なお、式(1)で明らかなように集光角Θを大きくすることでも分解能は向上するが、電子線は対物レンズの収差をゼロにできないため到達分解能が制限される。これを図4に示す。透過電子顕微鏡の分解能は球面収差係数と波長より式(2)で表され、この原理からも入射光の波長を短くすることが重要である。

図3 Resolution of optical beam

図4 Resolution of transmission electron microscope

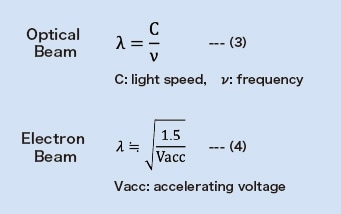

光の波長、電子線の波長は各々式(3)、(4)より求められる。光は振動数、電子は加速電圧を変数とする式で近似できる。

図5は式4を用い、SEMの使用領域である加速電圧5 ~ 30 KVで計算した電子線波長である。このとき波長は0.2 nm ~ 0.5 nmであり、発熱解析やIR-OBIRCHで使用する近赤外光と比較して大幅に波長を小さくできることが分かる。以上より分解能向上を見込んで電子線を使う技術を検討した。

図5 Comparison between optical beam and electron beam

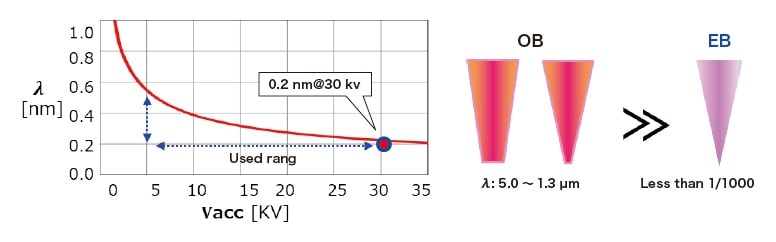

電子線を使う技術として、Nano-ProberによるEBAC(電子ビーム吸収電流法)が知られている。電子線を試料に走査(SCAN)し、金属配線に吸収される電流(吸収電流)を検出する。Probing経路が等電位にハイライトされるため配線経路の断線などOpen欠陥に有効な手法である。さらに電子線がSi基板に照射されると電子-正孔対が生成されるためEBIC(電子線誘起電流)を検出することも可能である。

図6にEBACの概要と事例を示す。

図6 EBAC overview and image

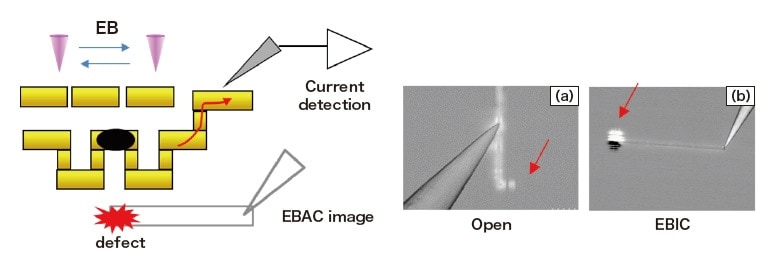

反面、EBACは等電位経路を可視化する手法であるためShort欠陥を絞り込むことは困難である。図7はEBACによるShort不良解析事例である。写真(c)は配線Layer、(d)はTr-LayerのShort不良であり、どちらもEBACではShort経路全体が反応してしまい、欠陥箇所判別が困難である。

図7 Short analysis image by EBAC

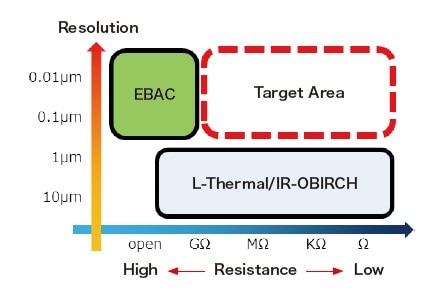

図8に現行解析手法における絞り込み分解能と検出可能な抵抗値を示す。抵抗性欠陥をμ m以下に絞り込む領域が本評価のターゲットである。

図8 Resolution and Defect resistance value

解決策として、EBAC 法にバイアス印加可能な“電圧印加型電子ビーム吸収電流法”(以下DI-EBAC)に着目した。理由はバイアス印加によりShort不良状態を確実に再現できること、かつ再現状態でEBACすることにより欠陥箇所の状態変化を電流変化としてより正確に捉えられると判断したからである。

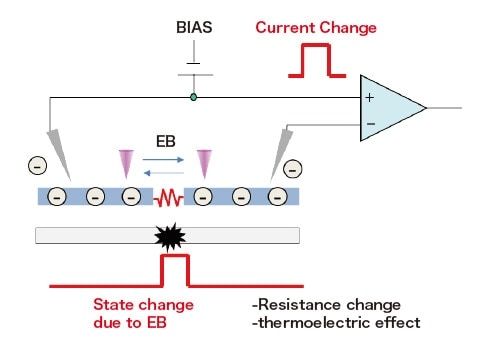

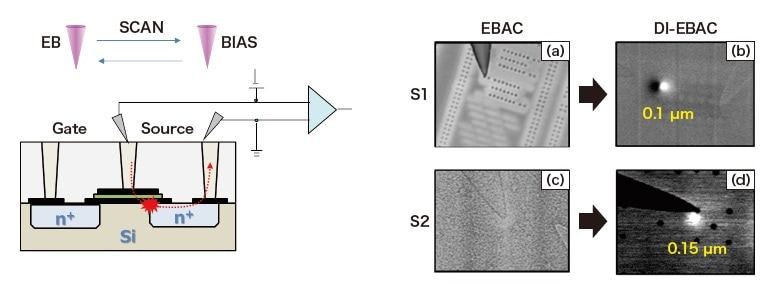

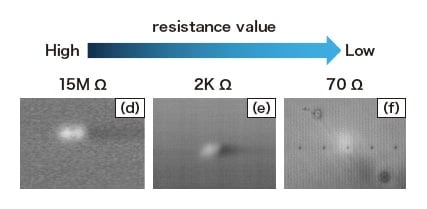

図9にDI-EBACの概要を示す。現行EBACにバイアス印加機能が追加されている。欠陥想定経路にバイアス印加した状態でEBACと同様に電子線を走査する機構である。

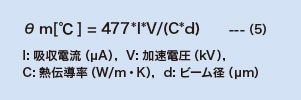

反応原理は、電子線が試料に到達すると照射箇所にはCastaingの理論より式(5)で算出される温度上昇が生じることが知られている。この温度変化により欠陥箇所に熱起電力・熱抵抗変化による電流変化が生じ、アンプで検出する。

図9 Principle of DI-EBAC

DI-EBACの有効性の検証として以下3項目が重要である。

上記のうち、①分解能は既に2-1. で記述した通り電子線の集束で求められる。電子線は1 nm以下に波長を小さくできるため光学解析より高分解能が期待できる。本評価のターゲットは、絞り込み後に断面解析できる領域、すなわちSTEM透過観察可能な0.2 μm以下とした。

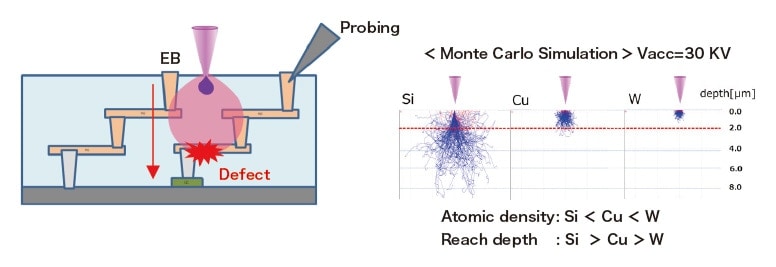

②透過性に関して、図10にEBACの模式図と電子線広がり模様を示す。図示した欠陥を検出するには電子線が上層Layerを透過して欠陥箇所に到達する必要がある。この電子線の潜りこみ特性は加速電圧と素材の原子密度に起因し、下記Monte Carlo Simulationで求められる。加速電圧30 KVであればCuバルクでも数μmまで潜り込むことが分かっており、CMOSイメージセンサが配線3 ~ 5層であることから下層Layerまで十分到達可能と考えられる。

図10 Electron beam transmission characteristics

最後に③印加バイアスの影響であるが、EBAC像が照射電子線によって構成されるため、印加する電流はノイズとなり感度に影響すると考えられる。

印加電流が感度に影響を与えない条件設定が重要と想定され、これらは照射光源がLaserであるOBIRCH法との大きな違いである。

以上より検証実験を行った。

図11はGate不良を用いた検証結果である。Gate破壊が想定されるSampleS1、S2に対し、Gate及びSourceコンタクトを露出してProbing、バイアスを印加している。写真(a)、(c)はS1、S2を各々現行EBACで測定した像であり、素子領域全体が反応してしまい明確に絞れていない。一方、写真(b)、(d)はDI-EBAC像であり、0.10~0.15 μmの局所反応が得られている。

図11 DI-EBAC result for gate leak defect

さらに図12はS1のDI-EBAC反応箇所を断面解析した事例である。写真(f)のSTEM像ではWコンタクトとSi基板のShortが確認できる。電子線照射により異種素材Short箇所にゼーベック反応による熱起電力発生、電流変化として検出した結果である。以上よりDI-EBACは想定通りの高分解能を有し、Short欠陥解析に有効と分かった。

図12 Cross-sectional image of reaction part

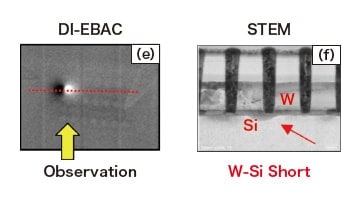

次に隣接配線間のShort不良を用いた検証結果である。図13に示すように不良想定Layerにつながる配線を露出しProbingしている。露出部は欠陥をロストしないようチップ端を部分開口している。写真(a)はDI-EBAC像であり、図示したように上層から4層目の欠陥を検出できており、この箇所には製造ラインの欠陥検査により複数配線にまたがる形成異常が確認されている(写真b)。さらに写真(c)は欠陥ではないがProbing経路につながるTrのEBIC反応である。このようにSi基板からの電荷回り込みも確認できていることから、上層配線を透過して欠陥検出可能であることが裏付けられた。

図13 DI-EABC result for metal short defect

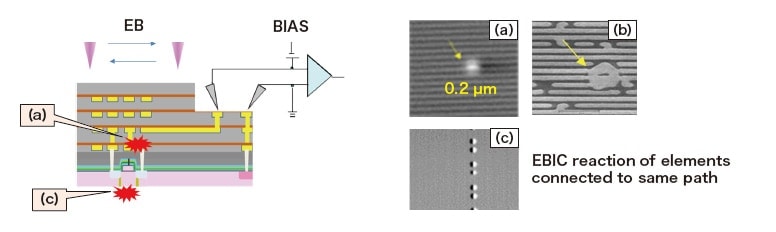

同様の検証方法で、抵抗値の異なる配線不良の測定結果を図14に示す。写真(d)から(f)にいくほど抵抗値が低いSampleであり、どれも明確に反応が得られている。とくに写真(f)は本評価で最も低い70Ωの欠陥であり、DI-EBACが高抵抗から低抵抗まで広い感度を持っていることが分かる。

図14 DI-EBAC Image by defect resistance value

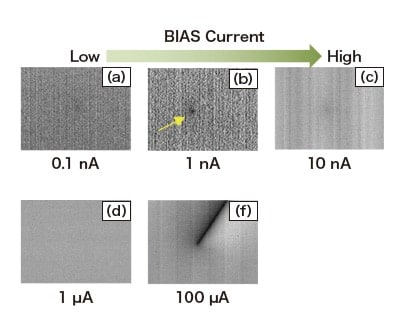

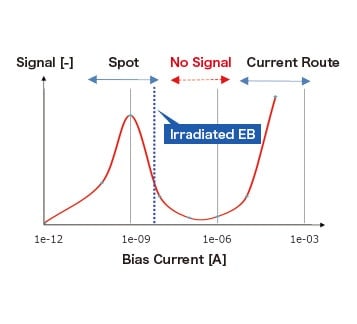

最後に試料に照射される電子線と印加バイアスの相互作用を検証した。まず電子線の照射条件であるが、試料に照射する電子線が大きいほど欠陥を活性するエネルギーが高いため装置Spec最大値30 μAに設定、この時試料表面に到達する電子線は実測値29 nAであった。この条件下で印加バイアスの電流値を変えながら各々DI-EBACを取得した。結果を図15に示す。印加電流ゼロでは無反応、写真(a)印加電流0.1 nA前後より反応が得られ、写真(b)1 nAで最も明確な反応が得られた。ここからさらに印加電流を増やし続けると(c)、(d)のように反応強度が低下、1 μAではほぼ無反応になった。この様子を反応箇所の輝度比と印加電流として図16にプロットした。輝度比は試料表面の電荷チャージを考慮して反応箇所と周辺領域の輝度差を抽出している。結果は、印加電流が照射電子線より小さいと輝度比が高く、逆に印加電流が大きいと輝度比が低下した。印加電流がノイズになりS/Nが低下して感度が下がるためと想定される。一方、印加電流を電子線より極端に大きく数百μA程度にすると写真(f)のように電流経路そのものがハイライトされた。電流が大きくなるほど磁場の影響で照射電子線の向きが変わりProbeより検出されたためと考えられ、印加電流の大きさで局所反応から電流経路全体に反応メカニズムが変わることが判明した。

図15 DI-EBAC Image by applied current

図16 EBAC Signal and Applied current

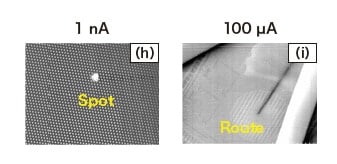

上述結果より、印加バイアスは照射電子線を考慮して適切にチューニングすることが重要であると分かった。図17は同じSampleに対し印加電流を変えて測定したDI-EBACとSEMの重ね合わせ画像である。印加電流1 nA時は写真(h)のような局所反応が得られ、100 μAでは写真(i)のような電流経路全体の反応が得られている。このように印加電流を使い分けることで二つのデータを容易に取得できることは欠陥箇所絞り込みに非常に有効な情報となる。

図17 Difference in reaction mode depending on applied current

本検証結果よりDI-EBACは以下のメリットを有し、CMOSイメージセンサ解析に有効な技術であることが分かった。

測定時には印加電流が検出感度へ影響をおよぼすため、装置条件を加味した適切な電流設定がポイントである。

電流印加による正確な不良再現性,電子線Stimulationによる高分解能と透過性を併せ持ち、現行手法と併用することでOpen欠陥からShort欠陥まで漏れなく対応できる解析環境を構築できる。

参考文献

著者紹介

片倉 康雄,辻田 順彦,山内 規義,河村 俊夫

ソニーセミコンダクタマニュファクチャリング株式会社